# DP CTS TOOLS DisplayPort<sup>TM</sup> compliance testing

## Full DP Compatibility Validation

Unigraf DP CTS Tools enable the user to reliably evaluate the compatibility of his equipment with VESA DisplayPort<sup>™</sup> Link Layer and HDCP standards. Unigraf DP CTS Tools provide more than only the pass / fail information. The on-screen and printable reports give a reliable and easy to understand explanation of the performance of the tested equipment on each step of the tests.

## Shortened Development Cycle

Early diagnosis of compliance issues will help to make the product implementation sound. By using Unigraf CTS Tools the testing of the functionality of the DP design will be a timely operation without unnecessary delays. The use of Unigraf DPA-400 AUX Channel Monitor will accelerate even more the achievement of this goal.

#### Benefits

- User friendly GUI

- Detailed HTML style reports

- Clear and precise error reporting

- EDID read / write

- DPCD read / write

- CTS LL and HDCP versions

- Test automation and manual modes

- Used by ATC Labs

- Use for Self Certification (upon approval)

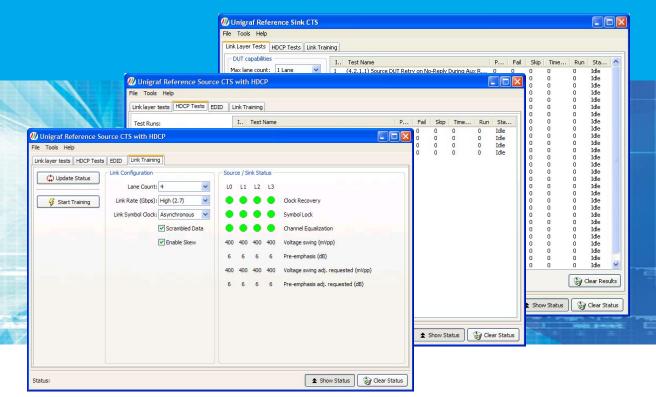

## Reference Source CTS Tool

Unigraf's Reference Source CTS Tool can be used with VTG-5225 DP units.

The tool GUI consists of the following seven task oriented dialogs. They are accessible through tabs or pull-down menus from the main dialog. The PC with CTS software is connected to both devices by using a RS-232 port. A separate USB to serial conversion cable can be used if a RS-232 port is not available.

#### **RefSource Dialogs**

- Link layer tests: LL test grid with result reporting

- HDCP tests: HDCP test grid with result reporting

- EDID: EDID view in HEX or decoded

- Link Training: Link training status and link configuration

- DPCD Read / Write: Access to DPCD register values

- Most Packed Timing: Selection of tested video timings

- Colorimetry: Definition of used video color formats

| 🕖 Unigraf Reference Source CTS   | with HDCP                                                       |                                  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------|----------------------------------|--|--|--|--|--|

| File Tools Help                  |                                                                 |                                  |  |  |  |  |  |

| Link layer tests HDCP Tests EDID | Link Training                                                   |                                  |  |  |  |  |  |

| Test Runs:                       | I Test Name P Fail                                              | Skip Time Run Sta                |  |  |  |  |  |

| 1                                |                                                                 | 0 0 0 Idle<br>0 0 0 Idle         |  |  |  |  |  |

| Unigraf Reference                |                                                                 |                                  |  |  |  |  |  |

| File Tools Help                  |                                                                 |                                  |  |  |  |  |  |

| Link layer tests HDCP Te         | sts EDID Link Training                                          |                                  |  |  |  |  |  |

| Test Runs:                       | I Test Name                                                     | P Fail Skip Time Run Sta         |  |  |  |  |  |

| 1                                |                                                                 | 0 0 0 0 0 Idle<br>0 0 0 0 0 Idle |  |  |  |  |  |

|                                  | 2 (28.02) Investige Descentions (Link Internity Check) 81 (     |                                  |  |  |  |  |  |

| File Table Hele                  |                                                                 |                                  |  |  |  |  |  |

|                                  | ests HDCP Tests EDID Link Training                              |                                  |  |  |  |  |  |

|                                  |                                                                 |                                  |  |  |  |  |  |

|                                  | EDID HEV contents EDID 1 3/1.                                   | 4 Decoder                        |  |  |  |  |  |

| 🔁 La                             | WUnigraf Reference Source CTS with HDCP<br>File Tools Help      |                                  |  |  |  |  |  |

|                                  |                                                                 |                                  |  |  |  |  |  |

|                                  |                                                                 | Source / Sink Status             |  |  |  |  |  |

| Quer                             |                                                                 | L0 L1 L2 L3                      |  |  |  |  |  |

| Status:                          |                                                                 |                                  |  |  |  |  |  |

| Most Packed timing modes se      |                                                                 | Clock Recovery                   |  |  |  |  |  |

| Most packed timing for 1 lane:   |                                                                 | Symbol Lock                      |  |  |  |  |  |

|                                  | Refresh rate Interlace/Progressive Blanking m bpp Packing ratio | P 🔍 Channel Equalization         |  |  |  |  |  |

| CVT 1280 800 6                   | Colorimetry                                                     | 400 400 400 Voltage swing (mVpp) |  |  |  |  |  |

| DMT 800 600 6                    | Format Bit Depth Dynamic Range Color Coeff.                     | 6 6 6 Pre-emphasis (dB)          |  |  |  |  |  |

| DMT 1024 768 6                   | RGB 6 VESA -                                                    | DPCD Read / Write                |  |  |  |  |  |

| Most packed timing for 2 lanes:  | RGB 8 VESA -                                                    |                                  |  |  |  |  |  |

| Standard H-Res V-Res F           | □ RGB 10 VE5A -<br>□ RGB 8 CEA -                                | Source / Target Address:         |  |  |  |  |  |

| DMT 1280 1024 6                  | RGB 10 CEA -                                                    | Data:                            |  |  |  |  |  |

| DMT 1360 768 6                   | VCbCr422 8 CEA ITU.601                                          |                                  |  |  |  |  |  |

| CVT 1280 800 6                   | VCbCr422 10 CEA ITU.601                                         |                                  |  |  |  |  |  |

| DMT 1400 1050 6                  | VCbCr422 8 CEA ITU.709                                          | Previous Op: None                |  |  |  |  |  |

| 🔲 🛄 DMT 1280 768 6               | CEA ITU.709                                                     |                                  |  |  |  |  |  |

| CVT 1600 1200 6                  | VCbCr444 8 CEA ITU.601                                          |                                  |  |  |  |  |  |

| Most packed timing for 4 lanes:  | YCbCr444 10 CEA ITU.601                                         |                                  |  |  |  |  |  |

| Standard H-Res V-Res F           | YCbCr444 8 CEA ITU.709     YCbCr444 10 CEA ITU.709              |                                  |  |  |  |  |  |

| CVT 2048 1536 6                  | E 10.709                                                        | ★ Show Status 🚱 Clear Status     |  |  |  |  |  |

| DMT 1792 1344 6                  |                                                                 | Thow status                      |  |  |  |  |  |

| DMT 1600 1200 6                  |                                                                 |                                  |  |  |  |  |  |

|                                  |                                                                 |                                  |  |  |  |  |  |

|                                  | Cancel 🖌 Acce                                                   | pt                               |  |  |  |  |  |

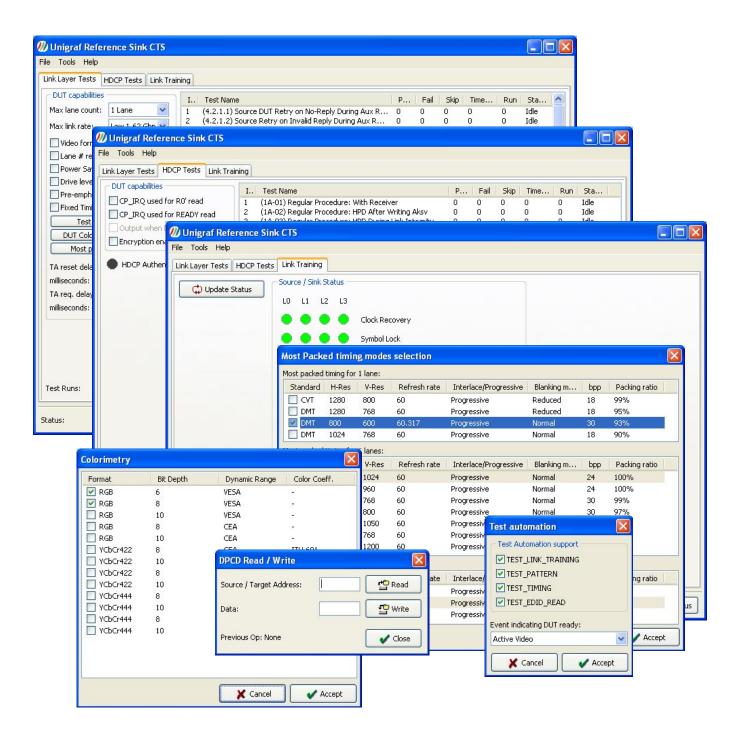

## Reference Sink CTS Tool

Unigraf's Reference Sink CTS Tool can be used with either the DPR-100 or the UFG 04 DP frame grabber. The functionality of the CTS tool is identical between the two devices.

The tool GUI consists of the following seven task oriented dialogs. They are accessible through tabs or pull-down menus from the main dialog. The PC with CTS software is connected to to the UFG 04 DP using a RS-232 port and to the DPR-100 through a USB port.

#### **RefSink Dialogs**

- Link layer tests: LL test grid with result reporting

- HDCP tests: HDCP test grid with result reporting

- Link Training: Link training status

- DPCD Read / Write: Access to DPCD register values

- Most Packed Timing: Selection of tested video timings

- Colorimetry: Definition of used video color formats

- Test automation: Definition of DUT capabilities

## DP CTS Tools DisplayPort<sup>™</sup> compliance testing

#### **DisplayPort Sink Compliance Test Report**

| CONTENTS                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |        |   |           |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|---|-----------|---------|

| Test Summary<br>General Information                                                                                                                                                                                                                                                                                                                                    | TEST SUMMARY                                                                                                 | DACCED |   | TIMED OUT | CHIDDED |

| View all test details View details by test 1 (-5.2.1.3) Read One Byle 1 ↑ 2 (-5.2.1.2) DPCD Receiver (- 3 (-5.2.1.3) Write Nine Byles 5 (-5.2.1.5) Write Nine Byles 5 (-5.2.1.5) Read One EDD I 7 (-5.2.1.7) EDD Read (1 Byles 6 (-5.2.1.6) Read One EDD I 7 (-5.2.1.7) EDD Read (1 Byles 6 (-5.2.1.6) Regal Aux Requi 9 (-5.2.1.8) Gitch Rejection ♥ Printer Friendly | 1 - (5.2.1.1) Read One Byte from Valid<br>DPCD Address                                                       | 1      | 0 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 2 - (5.2.1.2) DPCD Receiver Capability<br>Read (Read Twelve Bytes from Valid<br>DPCD Address)                | 1      | 0 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 3 - (5.2.1.3) Write One Byte to Valid<br>DPCD Address                                                        | 1      | 0 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 4 - (5.2.1.4) Write Nine Bytes to Valid<br>DPCD Addresses                                                    | 1      | 1 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 5 - (5.2.1.5) Write EDID Offset (One Byte<br>I2C-Over-Aux Write)                                             | 1      | 0 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 6 - (5.2.1.6) Read One EDID Byte (One<br>Byte I2C-Over-Aux Read)                                             | 1      | 0 | 0         | 0       |

|                                                                                                                                                                                                                                                                                                                                                                        | 7 - (5.2.1.7) EDID Read (1 Byte<br>12C-Over-Aux Segment Write, 1 Byte<br>12C-Over-Aux Offset Write, 128 Byte | 1      | 0 | 0         | O       |

#### **Tool Structure**

(

Unigraf DP CTS Tools provide the functionality required for Unigraf Reference Sink or Reference Source Test Equipment to conduct the compliance tests of DisplayPort<sup>™</sup> Link Layer and HDCP. They execute the full CTS test as required by VESA DisplayPort™ Link Layer Compliance Test Specification.

The DP CTS tools consist of two components: the Windows graphical user interface and the target firmware for the DisplayPort™ controller located on the Test Equipment. The actual tests are implemented by the firmware, while system control and status reporting are done by the user interface. The GUI and the FW are communicating using a serial interface. The firmware implements both the functions needed in the CTS tests and the normal functionality as DP video generator or frame grabber.

The tools can generate detailed HTML test reports and may include both Link Layer and HDCP compliance tests.

### Specifications

| Contents                     | Graphical User Interface and DP inteface controller (DPTx or DPRx) Firmware                       |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| HW interface                 | STM gm 60028 (Tx), gm 68020 (Rx)                                                                  |  |  |

| RefSource CTS<br>RefSink CTS | VTG-5225 DP pattern genarator<br>UFG-04 DP frame grabber, DPR-100                                 |  |  |

| Communication                | RS-232C (VTG-5225 DP and UFG-04 DP), USB 2.0 (DPR-100)                                            |  |  |

| Operating System             | Windows XP                                                                                        |  |  |

| Standard                     | Certified for testing to VESA DisplayPort™<br>Link Layer Compliance Test Standard,<br>Version 1.1 |  |  |

UNIGRAF OY

Ruukintie 3, FI-02330 Espoo, Finland Tel +358 9 859 550, fax +358 9 802 6699 UNIGRAF-USA Tel +1 888 362 7960, fax +1 605 362 7961 www.unigraf-us.com

Please visit www.unigraf.fi for listing of Unigraf Worldwide Distribution